基于FPGA的總線型LVDS通信系統(tǒng)設(shè)計

隨著現(xiàn)代通信技術(shù)的發(fā)展,高速數(shù)據(jù)傳輸需求日益增長,LVDS(低電壓差分信號)技術(shù)因其高速度、低功耗和強抗干擾能力,在通信系統(tǒng)中得到廣泛應用。結(jié)合FPGA(現(xiàn)場可編程門陣列)的靈活性和可重構(gòu)性,設(shè)計總線型LVDS通信系統(tǒng)能夠有效滿足復雜應用場景的需求。本文將圍繞系統(tǒng)設(shè)計的關(guān)鍵環(huán)節(jié)展開,包括總體架構(gòu)、硬件實現(xiàn)、軟件開發(fā)和測試驗證。

一、系統(tǒng)總體架構(gòu)設(shè)計

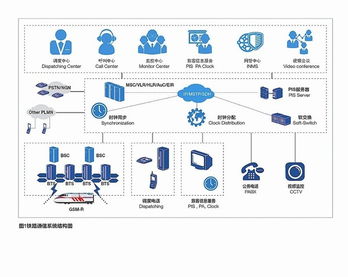

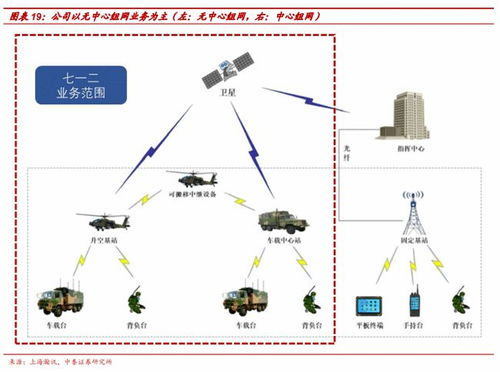

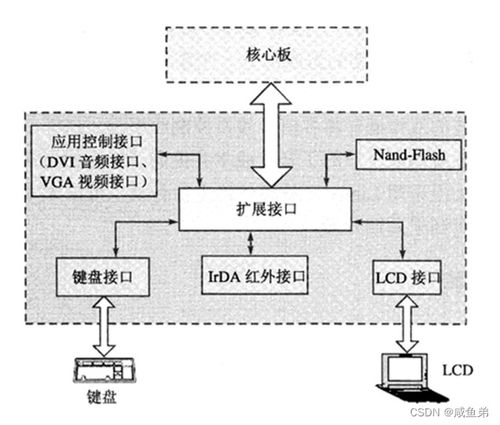

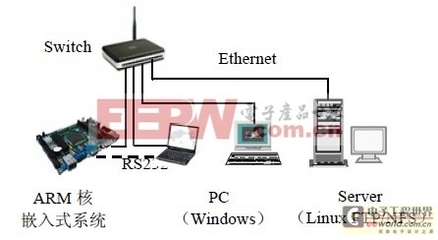

總線型LVDS通信系統(tǒng)基于FPGA作為核心控制器,通過LVDS接口實現(xiàn)多節(jié)點間的數(shù)據(jù)交換。系統(tǒng)架構(gòu)主要包括FPGA主控模塊、LVDS收發(fā)模塊、總線仲裁模塊和外部接口模塊。FPGA負責數(shù)據(jù)封裝、協(xié)議解析和時序控制;LVDS收發(fā)模塊采用差分信號傳輸,確保信號完整性;總線仲裁模塊管理多個節(jié)點的訪問權(quán)限,避免沖突;外部接口模塊連接傳感器或其他設(shè)備,實現(xiàn)數(shù)據(jù)采集與輸出。這種架構(gòu)支持點對多點的通信模式,適用于工業(yè)自動化、汽車電子和醫(yī)療設(shè)備等領(lǐng)域。

二、硬件設(shè)計與實現(xiàn)

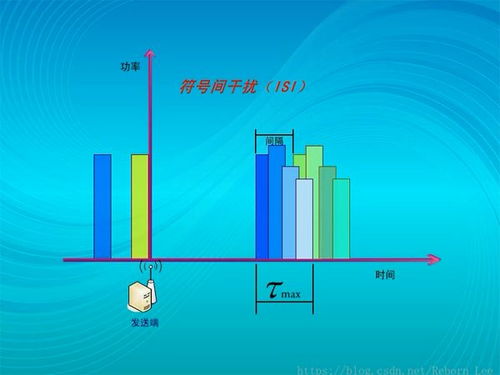

硬件設(shè)計是系統(tǒng)開發(fā)的基礎(chǔ),重點在于FPGA選型、LVDS接口電路和PCB布局。選擇高性能FPGA芯片,如Xilinx的Artix-7系列或Intel的Cyclone系列,這些芯片內(nèi)置LVDS收發(fā)器,支持高速數(shù)據(jù)傳輸(通常可達數(shù)百Mbps至Gbps級別)。LVDS接口電路需遵循差分信號設(shè)計原則,包括阻抗匹配、終端電阻和屏蔽措施,以減少信號反射和電磁干擾。PCB布局時,應保持差分線對等長、等距,并避免交叉干擾。電源管理模塊需提供穩(wěn)定電壓,確保FPGA和LVDS電路正常工作。通過仿真工具(如HyperLynx)進行信號完整性分析,可提前發(fā)現(xiàn)潛在問題,優(yōu)化設(shè)計。

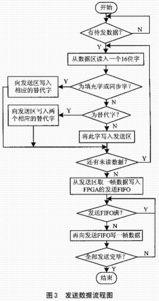

三、軟件開發(fā)與協(xié)議設(shè)計

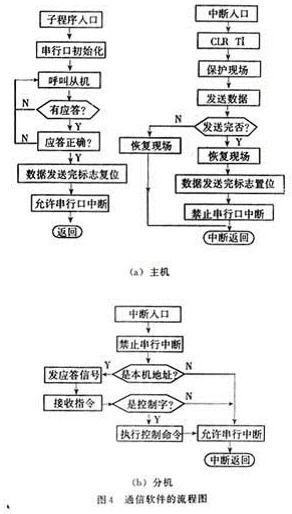

軟件開發(fā)涉及FPGA的編程和通信協(xié)議定義。使用硬件描述語言(如Verilog或VHDL)實現(xiàn)FPGA邏輯功能,包括數(shù)據(jù)編碼/解碼、時鐘同步和錯誤檢測。例如,采用8B/10B編碼提高數(shù)據(jù)傳輸可靠性,添加CRC校驗機制應對誤碼。協(xié)議設(shè)計需定義幀結(jié)構(gòu),包括起始位、地址字段、數(shù)據(jù)載荷和結(jié)束位,以支持總線通信。同時,開發(fā)上位機軟件(如基于C++或Python)用于監(jiān)控和調(diào)試,實現(xiàn)數(shù)據(jù)可視化與參數(shù)配置。在FPGA開發(fā)環(huán)境中(如Vivado或Quartus),進行綜合、布局布線和時序分析,確保代碼高效運行。

四、系統(tǒng)測試與性能驗證

系統(tǒng)開發(fā)完成后,需進行全面的測試驗證。使用示波器和邏輯分析儀測量LVDS信號質(zhì)量,檢查眼圖、抖動和噪聲水平。通過實際數(shù)據(jù)傳輸測試,評估吞吐量、延遲和誤碼率。例如,在實驗室環(huán)境中模擬多節(jié)點通信,測試總線仲裁機制的有效性。性能指標應滿足應用需求,如傳輸速率達到1Gbps以上,誤碼率低于10^{-12}。進行環(huán)境適應性測試,包括溫度、振動和電磁兼容性(EMC)測試,確保系統(tǒng)在惡劣條件下穩(wěn)定運行。根據(jù)測試結(jié)果,優(yōu)化硬件和軟件設(shè)計,提升系統(tǒng)可靠性。

基于FPGA的總線型LVDS通信系統(tǒng)設(shè)計結(jié)合了硬件與軟件的協(xié)同開發(fā),實現(xiàn)了高速、可靠的數(shù)據(jù)傳輸。通過合理的架構(gòu)規(guī)劃、精細的硬件實現(xiàn)和嚴格的測試流程,該系統(tǒng)可廣泛應用于高速工業(yè)網(wǎng)絡(luò)、汽車總線和醫(yī)療成像等領(lǐng)域。未來,隨著FPGA技術(shù)和LVDS標準的演進,該系統(tǒng)有望進一步集成AI功能,提升智能化水平。

如若轉(zhuǎn)載,請注明出處:http://m.hjz100.cn/product/26.html

更新時間:2026-02-24 16:01:25